Microprocessador

Contingut

Introducció[modifica]

Un Microprocessador (wikipedia) és un circuit integrat complex programable de propòsit general, que executa programes ubicats a la memòria RAM. Aquests programes consten d'instruccions per realitzar operacions lògiques i matemàtiques amb dades digitals.

Sol ser el "cervell" dels dispositius digitals actuals com PCs, mòbils, tablets, però també altres dispositius electrodomèstics com televisions, etc. que han passat del terreny analògic al digital.

Articles relacionats:

Arquitectura Von-Neumann[modifica]

El funcionament dels microprocessadors actuals es basa encara en el paradigma de l'arquitectura Von-Neumann (pronunciat "fon noiman"). Podeu llegir l'article de la Wikipedia com a referència.

Arquitectura externa[modifica]

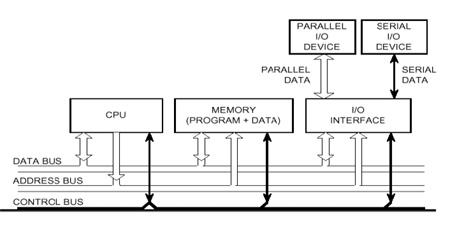

La CPU s'interconnecta mitjançant 3 busos:

- Bus d'adreces: on la CPU indica a quina adreça de memòria vol accedir.

- Bus de dades: on es transmeten les dades.

- Bus de control: senyals vàries per mantenir una transmissió en ordre i sense errors.

La CPU internament[modifica]

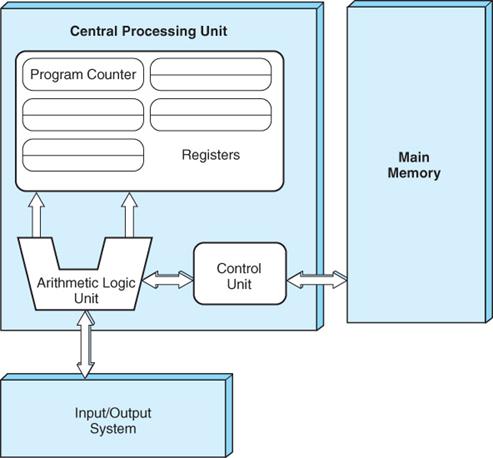

La CPU disposa de:

- UC - Unitat de Control: governa el funcionament general del dispositiu.

- ALU - Arithmetic-Logic Unit: realitza els càlculs i operacions lògiques.

- Registres interns:

- Registres de DADES: contenen dades descarregades de la RAM o dels perifèrics.

- Solen numerar-se com a A, B, C, etc.

- Registres de CONTROL: serveixen per governar el comportament de la CPU.

- PC - Program Counter: porta el control de l'execució, indicant quina instrucció del programa s'està executant.

- IR - Instruction Register: és on s'emmagatzema la instrucció per després ser executada.

- Registres de DADES: contenen dades descarregades de la RAM o dels perifèrics.

Execució de programes en la CPU[modifica]

Les CPUs son capaces d'executar una sèrie d'instruccions de baix nivell, que vol dir que són instruccions molt senzilles i fortament depenents del hardware. La versió Assembler d'aquestes instruccions solen indicar-se amb mnemotècnics com LOAD (carrega), ADD (suma), MUL o PROD (multiplica/producte), JP (jump=salt) i similars.

En canvi, els llenguatges d'alt nivell es caracteritzen per tenir una major abstracció i ser més independents del hardware subjacent. Faciliten molt la llegibilitat i s'assemblen més al llenguatge natural humà. La CPU no pot executar directament aquests programes, abans cal compilar-los o bé han de ser executats per un intèrpret. La CPU sempre executa instruccions de baix nivell.

Podeu veure un estupendu simulador aquí:

http://lab.xitrus.es/VonNeumann/

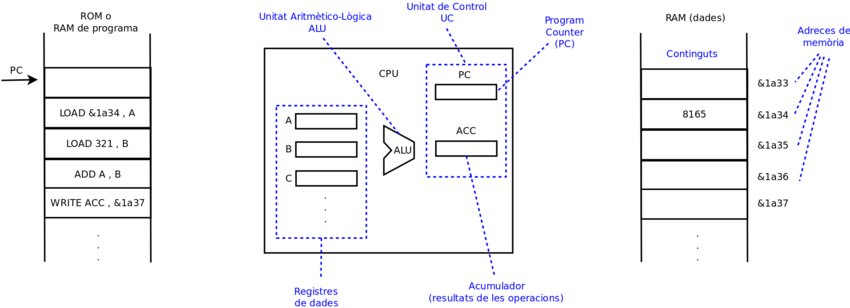

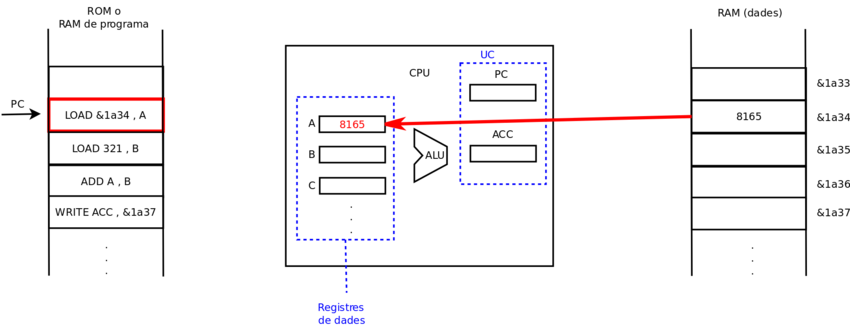

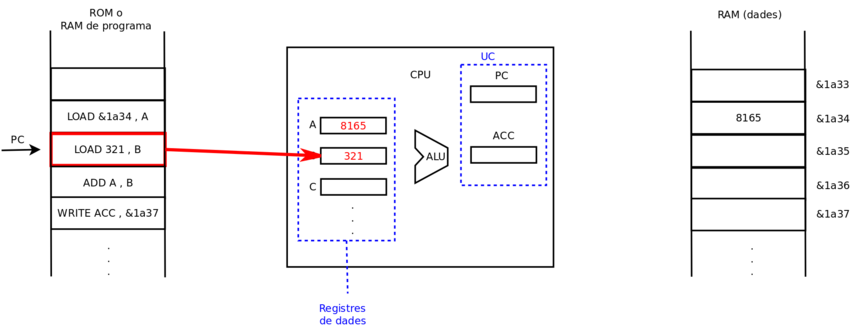

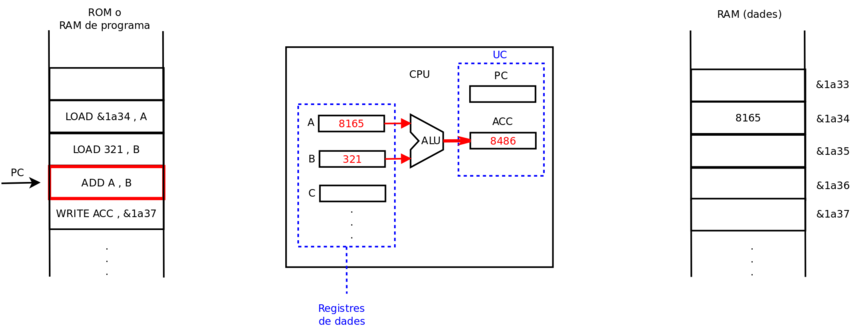

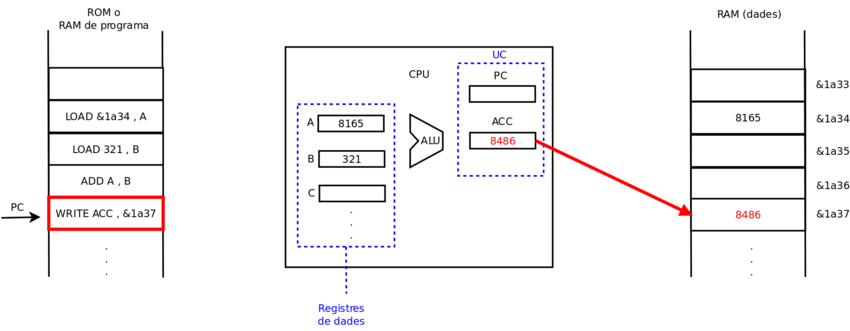

En la següent seqüència observem com s'executen les instruccions del programa seqüencialment.

Podem distingir clarament dues regions de memòria:

- Memòria de programa: els programes s'emmagatzemen en una regió de la RAM. En les màquines dedicades (p.ex. expenedores de begudes) o més senzilles sol estar en una ROM o Read-Only Memory (no-volàtil, i.e., no s'esborren quan s'apaguen).

- Memòria de dades: una altra regió de la RAM conté les dades a tractar (text a tractar, dades numèriques, etc.).

Exercici[modifica]

Si has entès els diagrames anteriors, fes els dibuixos de l'execució corresponent al següent programa, i intenta esbrinar quin és el missatge resultant que ens queda a la adreça &1000. El què hi ha després del ";" és un comentari i no és de la instrucció (no ho tingueu en compte).

WRITE 76, &1000 ;} LOAD 70, A ;} -> diagrama 1 LOAD 9, B ;} ADD A, B ; -> diagrama 2 WRITE ACC; &1001 ;} WRITE 86, &1002 ;} -> diagrama 3 WRITE 69, &1003 ;}

Realitza 3 diagrames a l'estil de les explicacions anteriors per indicar el comportament de cada instrucció. En el 1r pots posar les 3 primeres instruccions.

Transaccions de dades[modifica]

Diagrama de les transferències de dades en l'arquitectura Von-Neumann. Es poden veure la ocupació dels busos i les senyals de control.

En aquest exemple la CPU accedeix a la RAM per baixer el contingut d'una adreça.

Cal remarcar que l'activitat en els busos està governada pel CLOCK (rellotge).

La seqüència de LOAD (LD) o càrrega de dades de la RAM a la CPU està seqüenciada de la següent manera:

- La CPU pren la iniciativa i escriu al bus d'adreces la direcció que es vol obtenir.

- La CPU avisa la RAM que vol la dada amb els senyals de control MREQ i RD (Memory Request i Read).

- La RAM reconeix la demanda i demana a la CPU que s'esperi a través de la senyal de WAIT (espera).

- Quan la senyal de WAIT torna a 1, la dada està disponible al bus de DADES perquè la CPU el llegeixi.

Optimitzacions : DMA i interrupcions[modifica]

En el funcionament habitual de l'arquitectura Von-Neumann el control sempre el porta la CPU, però això ens porta a colls d'ampolla poc eficients.

La CPU és un dispositiu molt ràpid (el més ràpid), mentre que la memòria RAM és més lenta i el sistema de entrada/sortida (E/S) encara ho és més. Per tant, quan la CPU requereix l'entrada de dades del sistema d'E/S (per exemple d'un disc dur o un dispositiu USB com un ratolí) ha d'esperar-se i "malgasta" el seu temps.

Així, s'han inventat diverses optimitzacions per aprofitar tota la potència de la CPU i no fer-la esperar enfront dispositius lents.

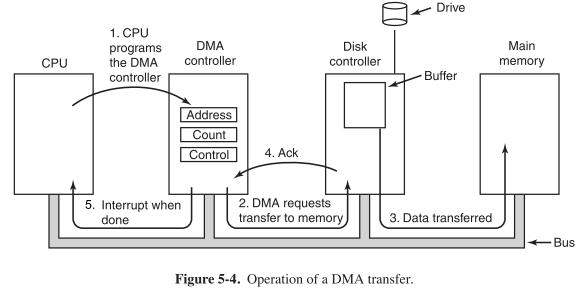

- DMA o Direct Memory Access: mecanisme per automatitzar la transferència de dades entre la RAM i el sistema d'E/S sense intervenció de la CPU.

- Interrupcions : sistema per avisar la CPU perquè interrompeixi la tasca actual i s'ocupi d'algun dispositiu extern d'E/S. Si no utilitzem interrupcions, la CPU es veu obligada a sondejar regularment els dispositius (polling) el que resulta molt més ineficient.