Diferència entre revisions de la pàgina «Microprocessador»

Salta a la navegació

Salta a la cerca

| Línia 8: | Línia 8: | ||

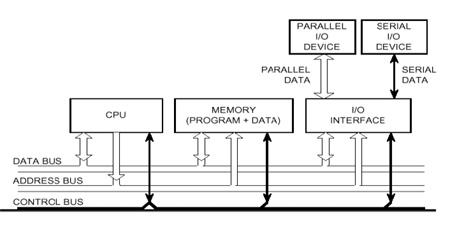

Us recordo que l'esquema vist a classe té una pinta com aquesta: | Us recordo que l'esquema vist a classe té una pinta com aquesta: | ||

| − | [[Fitxer:arquitectura-von-neumann.jpg]] | + | {| border="0" |

| + | |[[Fitxer:arquitectura-von-neumann.jpg]] | ||

| + | |[[Fitxer:esquema-microprocessador.jpg|300px]] | ||

| + | |} | ||

| + | |||

| + | Cal recordar que tenim 3 busos: | ||

| + | *Bus d'adreces: on la CPU indica quina adreça de memòria vol accedir. | ||

| + | *Bus de dades: on es transmeten les dades. | ||

| + | *Bus de control: senyals vàries per mantenir una transmissió en ordre i sense errors. | ||

| + | |||

| + | |||

| + | La CPU disposa de: | ||

| + | *'''UC - Unitat de Control''': governa el funcionament general del dispositiu. | ||

| + | *'''ALU - Arithmetic-Logic Unit''': realitza els càlculs i operacions lògiques. | ||

| + | *Registres interns: | ||

| + | **'''Registres de DADES''': contenen dades descarregades de la RAM o dels perifèrics. | ||

| + | ***Solen numerar-se com a A, B, C, etc. | ||

| + | **Registres de CONTROL: serveixen per governar el comportament de la CPU. | ||

| + | ***'''PC - Program Counter''': porta el control de l'execució, indicant quina instrucció del programa s'està executant. | ||

| + | ***'''IR - Instruction Register''': és on s'emmagatzema la instrucció per després ser executada. | ||

Revisió del 19:02, 22 oct 2010

De moment els apunts d'aquesta part els donaré a classe. Hi ha molts dibuixos: el més important és saber plasmar en dibuixos el funcionament del microprocessador.

Arquitectura Von-Neumann

El funcionament dels microprocessadors actuals es basa encara en el paradigma de l'arquitectura Von-Neumann (pronunciat "fon noiman"). Podeu llegir l'article de la Wikipedia com a referència.

Us recordo que l'esquema vist a classe té una pinta com aquesta:

|

|

Cal recordar que tenim 3 busos:

- Bus d'adreces: on la CPU indica quina adreça de memòria vol accedir.

- Bus de dades: on es transmeten les dades.

- Bus de control: senyals vàries per mantenir una transmissió en ordre i sense errors.

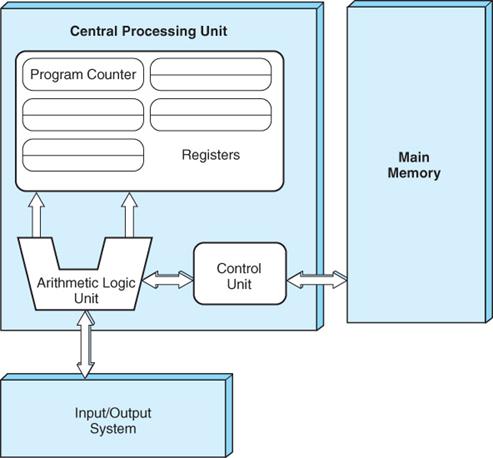

La CPU disposa de:

- UC - Unitat de Control: governa el funcionament general del dispositiu.

- ALU - Arithmetic-Logic Unit: realitza els càlculs i operacions lògiques.

- Registres interns:

- Registres de DADES: contenen dades descarregades de la RAM o dels perifèrics.

- Solen numerar-se com a A, B, C, etc.

- Registres de CONTROL: serveixen per governar el comportament de la CPU.

- PC - Program Counter: porta el control de l'execució, indicant quina instrucció del programa s'està executant.

- IR - Instruction Register: és on s'emmagatzema la instrucció per després ser executada.

- Registres de DADES: contenen dades descarregades de la RAM o dels perifèrics.

Transaccions de dades

Us passo un diagrama de les transferències de dades en l'arquitectura Von-Neumann.

Cal remarcar que l'activitat en els busos està governada pel CLOCK (rellotge).

La seqüència de LOAD (LD) o càrrega de dades de la RAM a la CPU està seqüenciada de la següent manera:

- La CPU pren la iniciativa i escriu al bus d'adreces la direcció que es vol obtenir.

- La CPU avisa la RAM que vol la dada amb els senyals de control MREQ i RD (Memory Request i Read).

- La RAM reconeix la demanda i demana a la CPU que s'esperi a través de la senyal de WAIT (espera).

- Quan la senyal de WAIT torna a 1, la dada està disponible al bus de DADES perquè la CPU el llegeixi.